I recommend Ham Radio Duo’s video on Morse Code Tools: CW Practice and Games (N4BKY & N4FFF) for a more detailed overview. Most of the tools here are covered in their video!

When learning CW there are many online practice tools:

- Morse Invaders (KE6EEK) – a simple game for practicing sending morse in a space-invaders style – very addictive!

- Morse Code AI Chat Bot (N4BKY & N4FFF) – an AI chatbot that sends and receives CW

- V-Band () and Vail () – online ham-band platforms where you can practice CW with others

- Morse Code Battleships (N4BKY & N4FFF) – an interactive battleships game with CW interface

I really also like MorseWalker (W6NCY), a joke on the contest practice software MorseRunner (VE3NEA). I really enjoy using MorseWalker – but it’s receive practice only.

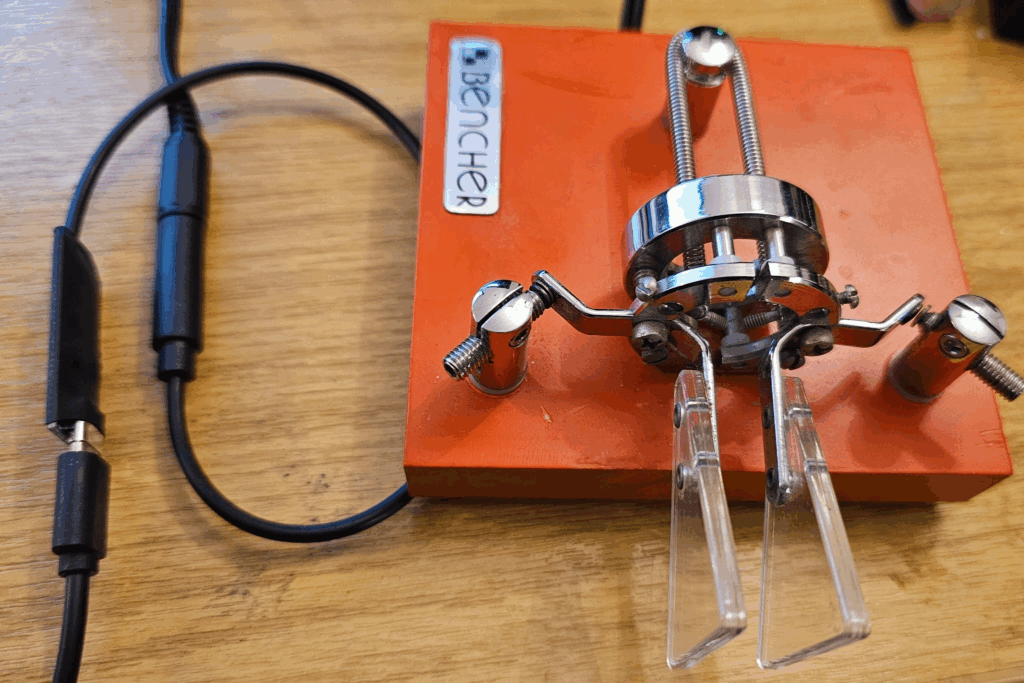

For those that need CW paddle input, you really want to be using an interface – that way, you can connect your favourite key (or, failing that, the key that you’ll be using) to your computer and practice sending with that key…

Interfacing Options

There are a couple of existing interfaces:

- The Vail Adapter is a full project with custom PCBs, etc., and works well.

- The VBand Adapter can be purchased from their site.

Because I am impatient and had the parts, I decided to build my own.

The Build

I took inspiration from the OZ1JHM’s hamradio-solutions-vband-interface code. I am mainly interested in the paddle operation, but, you could modify this code easily to just send a single keyboard-button press for the straight key.

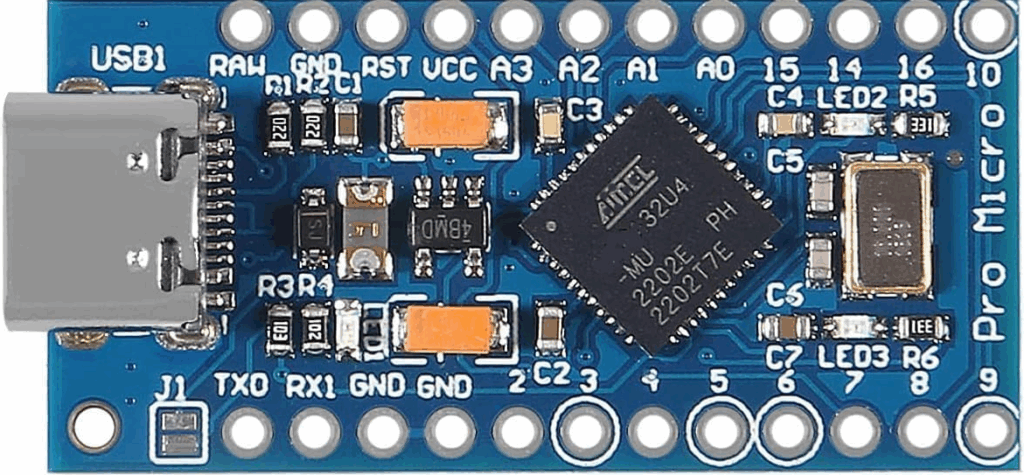

It’s important to note that you’ll need an Arduino where USB is directly connected to the Arduino chip and not via an UART IC since these only support UART ports and can’t emulate a keyboard. This means that you cannot use devices based around the Atmega328P.

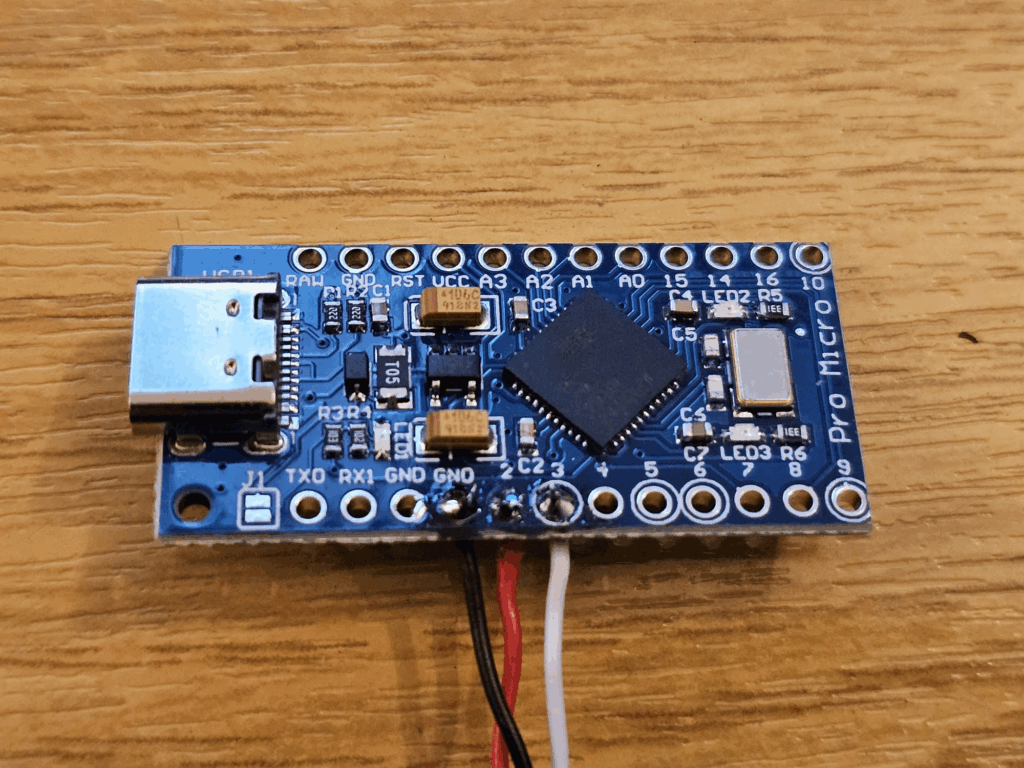

The code below is for an Arduino Pro Micro (I used a USB C version) which is based on the Atmega32U4:

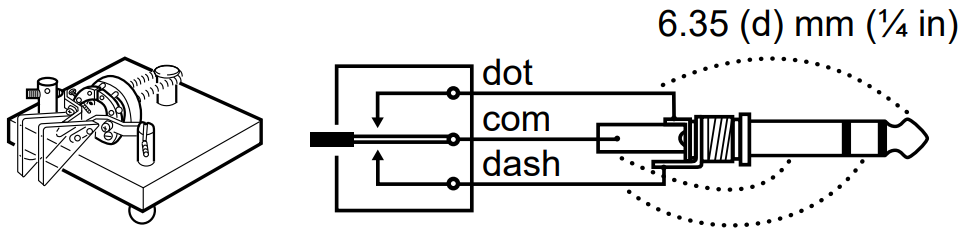

You’ll also need a way to connect your key easily. I used a moulded 3.5mm (1/8in) stereo socket on a short cable (available online cheaply) to create a nice connection, that would allow me to easily plug & unplug my key.

It is then fairly straightforward to make the 3 solder joints needed:

- Black: GND

- Red: A2 (dit)

- White: A3 (dah)

You may have to tinker around with the connections a little bit to get your radio, the adapter and your key to work interchangeably. Above is what it ended up being for me.

Above, taken from the manual of my Icom IC-7610. I have wired the Arduino to have the same polarity as the radio, assuming this to be the standard. Note, the radio uses a 6.35mm (1/4in) jack, not the smaller 3.5mm (1/8in) as we’re using.

And you’re ready to program the MCU! We’ll finish up with the hardware once we’ve checked it works!

Arduino Pro Micro Code

// Include the keyboard drivers

#include <Keyboard.h>

// Pin Definitions: Where the paddle pins connect.

// Note: Closing the contact should ground these pins.

# define DIT_PIN 2

# define DAH_PIN 3

// Arduino setup code

void setup() {

pinMode(DIT_PIN, INPUT_PULLUP); // en internal pullup (dit)

pinMode(DAH_PIN, INPUT_PULLUP); // en internal pullup (dah)

Keyboard.begin(); // start keyboard runtime

}

void loop() {

// While no paddle button is pressed, release all keys.

while (digitalRead(DIT_PIN) == HIGH && digitalRead(DAH_PIN) == HIGH){

Keyboard.releaseAll();

}

// On DIT pressed, send LEFT CONTROL key, else release

if ( digitalRead(DIT_PIN) == LOW){

Keyboard.press(KEY_LEFT_CTRL);

} else{

Keyboard.release(KEY_LEFT_CTRL);

}

// On DAH pressed, send RIGHT CONTROL key, else release

if ( digitalRead(DAH_PIN) == LOW){

Keyboard.press(KEY_RIGHT_CTRL);

} else{

Keyboard.release(KEY_RIGHT_CTRL);

}

// Wait 5ms

delay(5);

}Tidying it up!

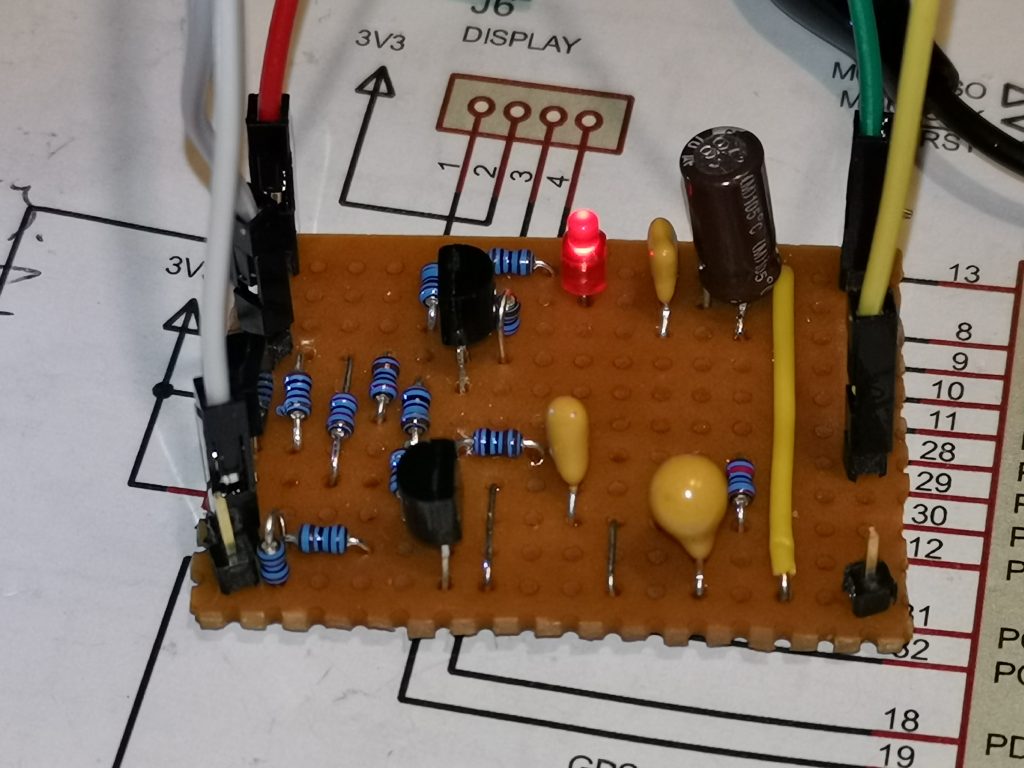

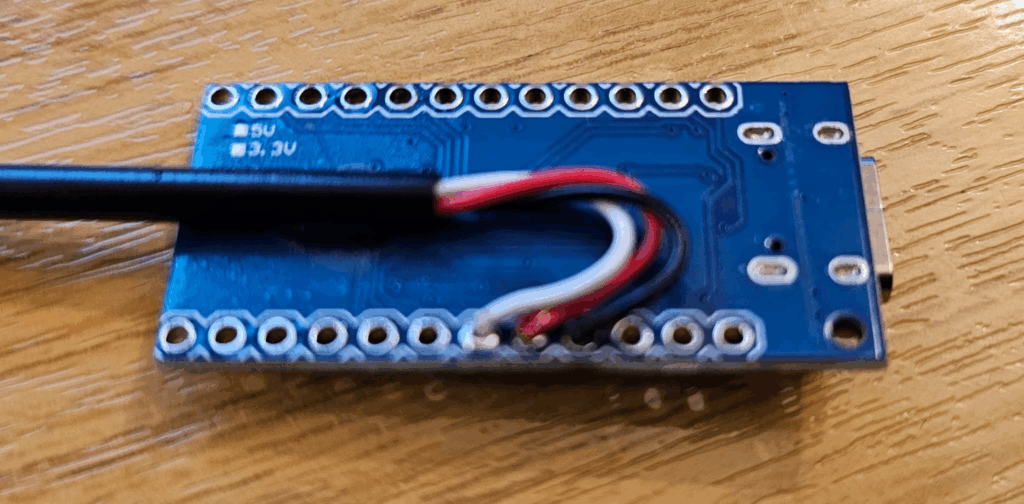

Once you’re happy it is working as you wish, an optional step for longevity is to protect the PCB. I did this by first applying a dot of super-glue to the cable and attaching it to the back of the PCB (note how I brought the wires out on that side).

Next I used some heatshrink tubing to cover the board, protecting everything.

And, you’re good to go!

With that, you’re ready! Connect your key, connect your USB cable, and you can practice until you’re CW is perfect!