Over the past few evenings, I have been experimenting with phase-frequency detectors. I have an upcoming project that requires the use of one, and, I figured I’d refresh my memory on them. I ended up using my Lattice MachXO2 breakout board as the development platform.

The first step was to divide a 10 MHz crystal oscillator down to 10 kHz. That was easily done with a counter, counting from 0 to 499, and then resetting to 0. Every reset would simultaneously toggle an output bit, with the net result being a square-wave clock on the output bit, periodic every 1000 cycles of the input. A divide by 1000 counter.

Next was to understand the Phase-Frequency Detector (PFD). This is commonly referred to as a Type 2 detector, since it detects not only phase difference but frequency difference. This means that the PLL will only ever lock to the fundamental frequency, and not harmonics. It also means that when the loop is unlocked, the PFD knows which way to drive the VCO to regain lock. A Type 1 detector only uses phase information, and so drives the oscillator in the direction of the phase difference until the loop locks – as a result, Type 2 detectors lock quicker.

The Type 2 detector has two outputs, up and down, which pulse for the required direction with a duty cycle proportional to the phase difference.

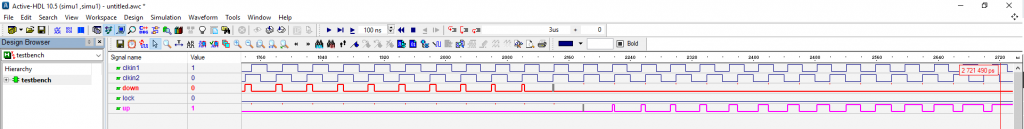

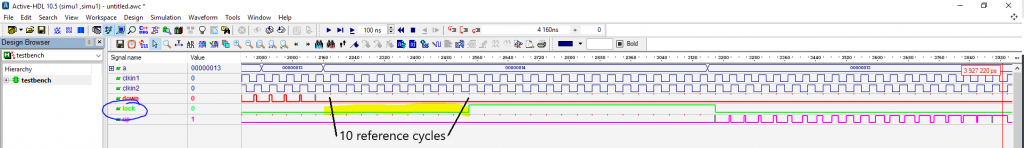

I spent a few days designing and simulating the PFD using the Aldec Active-HDL simulator to confirm that my circuit did indeed perform as expected:

I then added a simple lock detector, which set a locked signal high if the phases were in lock for the past 10 cycles as a proof of concept. In reality, a much longer observation window will be used. It is possible to see the lock signal becomes high after 10 cycles.

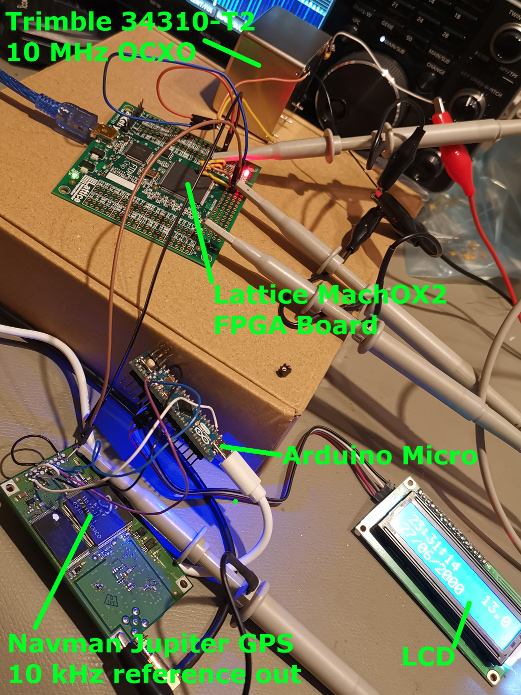

The final stage of this project snippet was to test on real hardware. The Verilog code was pushed through synthesis, place and route, and a configuration file for the Lattice FPGA generated. This was then programmed into the board, and the board taken to the lab – you can see all the main parts of the setup in the photo below.

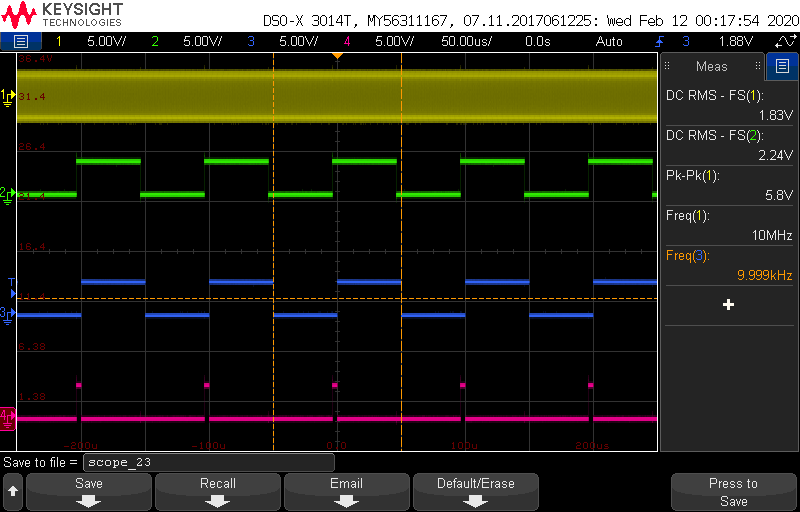

Below, you can see the scope traces from the probes in the lab bench photo. The yellow trace shows the 10 MHz VCO frequency from the Trimble 34310-T2 OCXO. The green trace is a debug from the FPGA output showing the 10 MHz signal divided down 10 kHz. The blue trace is GPS locked 10 kHz reference output. Finally, the purple is phase detector output, here from the ‘down’ output of the detector since we see that the divided VCO output (green) slightly leads the GPS reference (blue). The ‘up’ output is at logic-0 throughout.

The next part of the project was to create the charge pump circuit which converts the ‘up’ and ‘down’ pulsed signals into an analogue control voltage for the VCO.

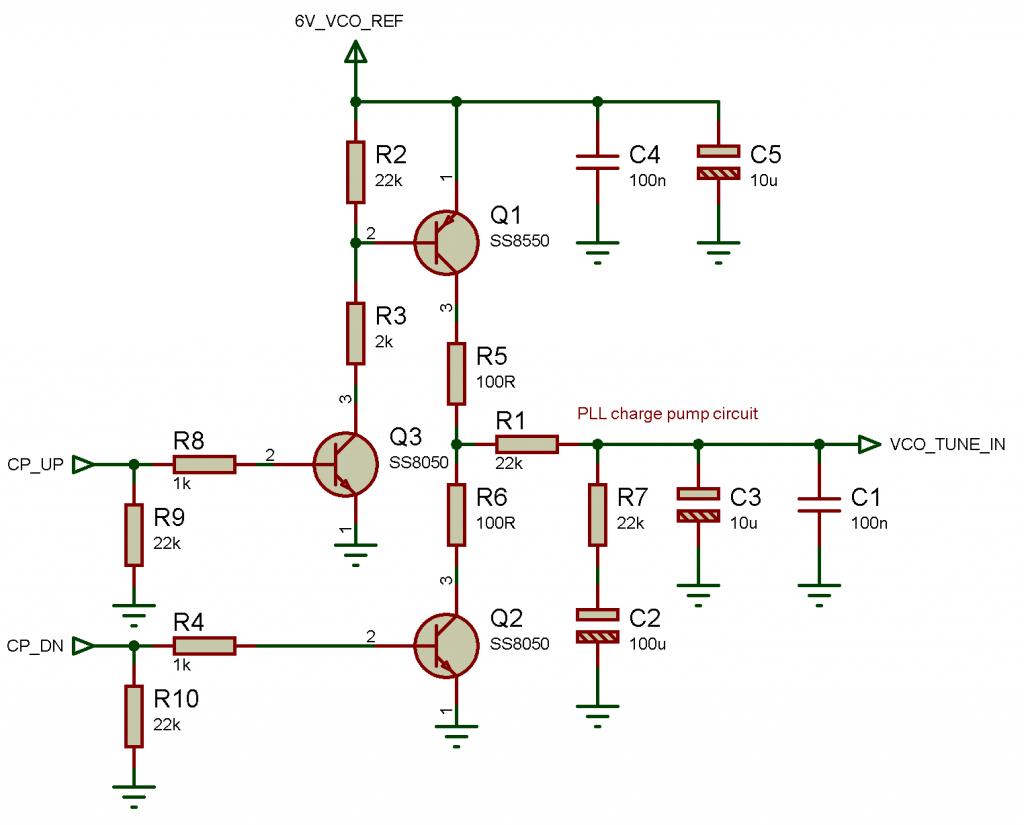

The parts for the charge pump took a few days to arrive, and while waiting I contrived the following circuit. Since the OCXO generates a 6V reference voltage for use with the VCO input (actually 5.4V in my case), it seemed wise to use that. Some crude experiments had lead me to a tune voltage of around 3.5V. The circuit uses a PNP transistor (Q1) to put pulses of energy into the filter network via R1. Similarly, it uses an NPN transistor (Q2) to remove pulses of energy from the filter via R1. R5 and R6 serve as a current limit in case both Q1 and Q2 are both powered. A further NPN transistor (Q3) acts as a voltage interface between the ~6V on the base of Q1 and the FPGA IO at 3V3 maximum. Only the values of components in the filter section are critical (R1, R7, C1, C2, C3); the others were chosen from what I had laying around.

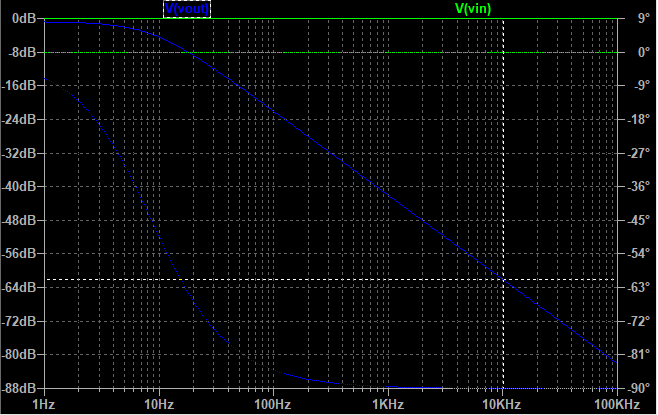

The loop filter was tested and tweaked in LTspice using the values above. The loop filter has around 62 dB of attenuation at 10 kHz (our reference [and thus up/down pulse] frequency).

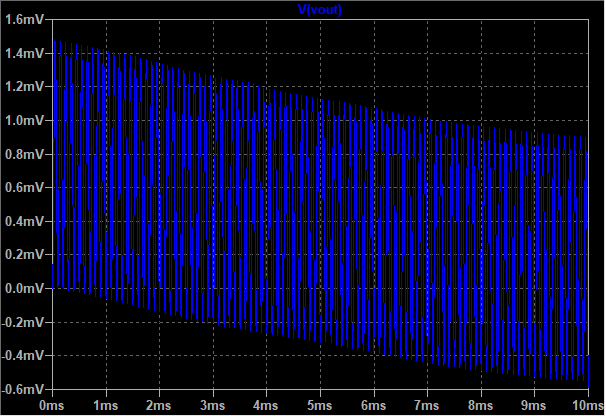

A look in the time domain shows we can expect about 1.5mVp-p at 10 kHz from visual estimation. An output of 1.5mVp-p is approximately 0.53 mVrms, which gives us around -66 dBV of attenuation (similar to we saw above). The curve of the waveform is the DC levels settling out at the start of the simulation.

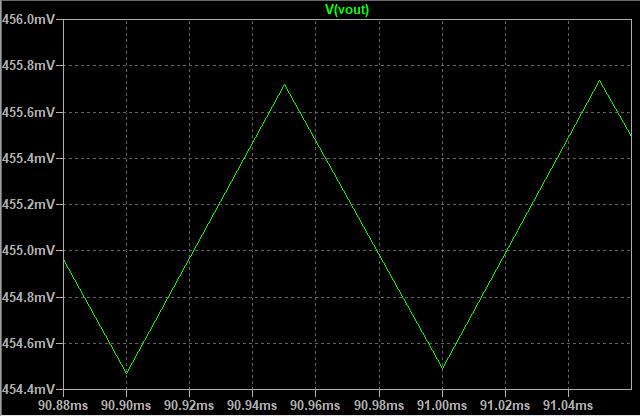

And finally the steady-state ripple; for a 1V square wave (0V-1V) input, a 1.23 mV ripple exists at the output (455.719-454.486).

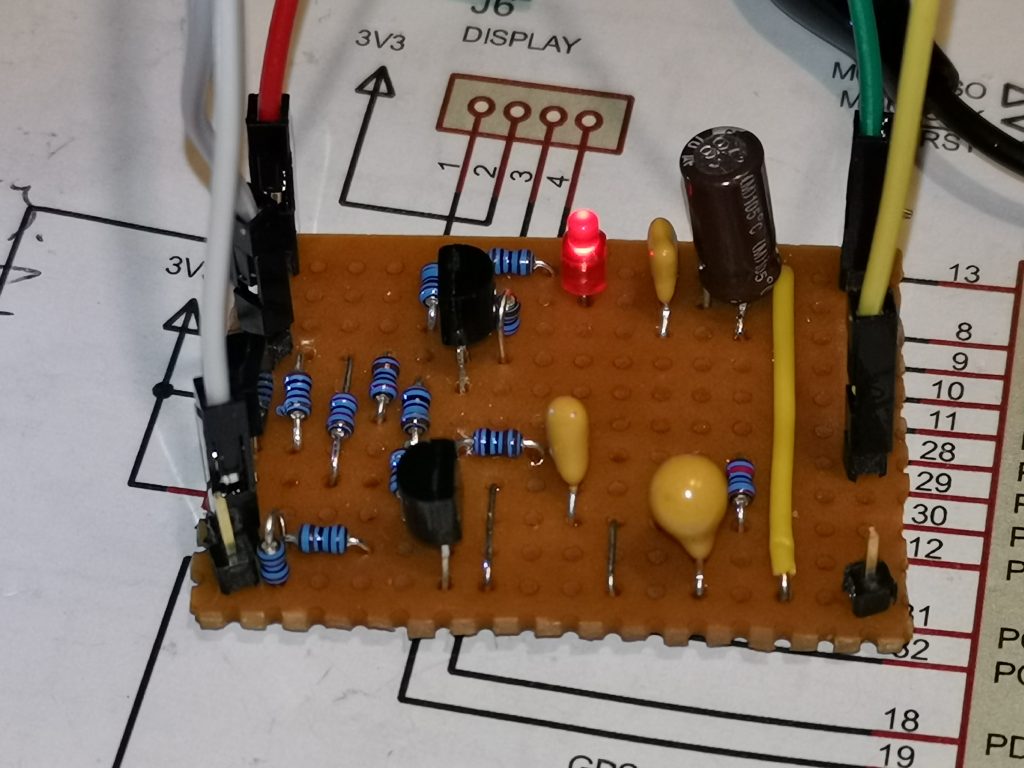

The penultimate step was to build the circuit and confirm it worked in real life. I made the charge pump on a scrap of strip-board, with pin headers for the main signals. On the left, +6V VCO reference input, the up and down signals from the FPGA, and on the right, ground and the VCO tuning input. The circuit is pretty much laid out as per the schematic, with the addition of an LED.

The final step was to watch the PLL lock on the scope! In the short video clip below, you can see the yellow trace is the 10 kHz reference frequency from the GPS. The green trace is the 10 MHz from the VCO. The blue trace is the 10 MHz divided down to 10 kHz. The purple trace is the VCO tune voltage – the output of the charge pump.

The closing remark is that this project was a learning exercise. The Verilog code & TB is presented here on GitHub and you’re invited to take a look.